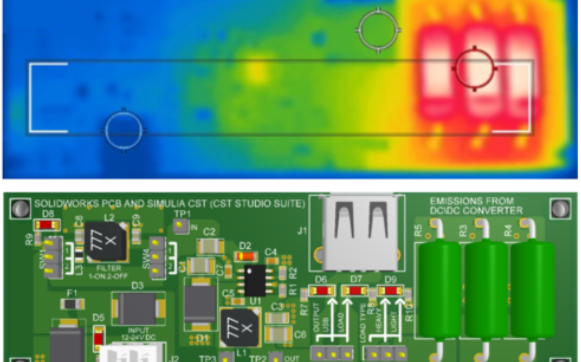

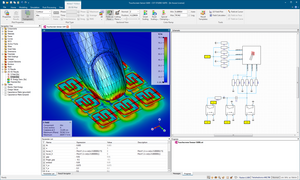

CST Studio Suite考虑ESD保护二极管元件的差分传输线的阻抗模拟

日期:2025-07-10 发布者: Richard SjiarielRichard 浏览次数:次

通过单根双绞线 (STP) 在发射器和接收器之间传输高带宽数据,需要在发射器和接收器侧添加额外的 ESD(静电放电)保护元件。这些保护元件安装在印刷电路板 (PCB) 上。对于6 Gbps的数据速率,PCB传输线的设计必须考虑信号完整性方面的ESD保护元件。在这篇博文中,我们介绍了 ESD 保护元件的影响,以及保持信号完整性所需的布局优化。最后,我们展示了仿真结果和测量结果之间的比较。

以下内容是与 Inova Semiconductors GmbH 的应用工程师 Reiner Welazer 合著的。他在 RF 和模拟信号 PCB 的信号和电源完整性以及 EMC 兼容设计方面拥有 20 多年的经验。近年来,他广泛研究电子电路的 ESD 保护,尤其是汽车。

耦合微带线建模

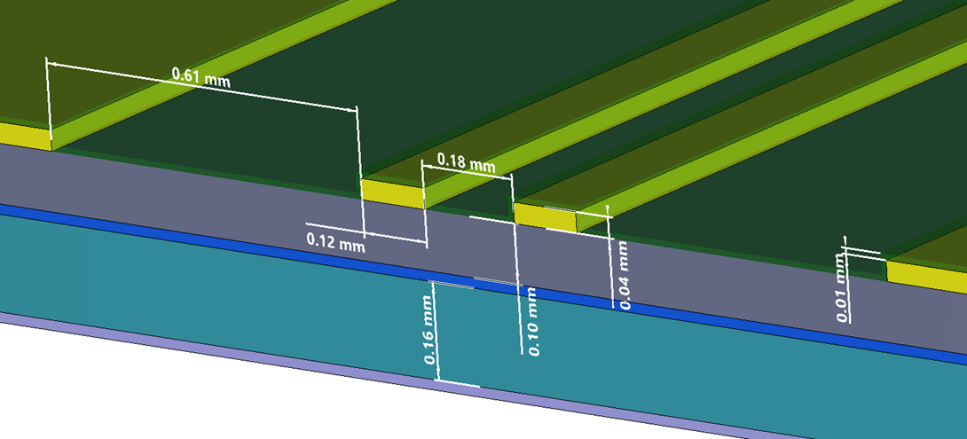

通过单根双绞线电缆进行数据传输,使用边缘耦合表面微带导体实现 PCB 上的连接。差分信号主要用于高速数据传输。这提供了良好的电磁兼容性 (EMC)。通常,使用标称线路阻抗为 100 Ω 的边缘耦合表面微带导体,并位于 TOP 层。图 1 显示了用于仿真的边沿耦合微带线的尺寸,可提供 100 欧姆的差分线阻抗。

图 1.具有维度的差分线模型

对于线路阻抗计算,正确的材料属性和正确的阻焊层形状的建模非常重要。如图 1 所示,阻焊层的建模实现为覆盖微带导体的薄皮。

由于差动线通过插头连接到电缆,因此该插头极有可能发生 ESD 事件。这种 ESD 事件在短时间内 (< 1 ns) 产生非常高的电压和电流峰值,并可能对电子元件造成损坏。为避免这种情况,ESD 保护元件应连接到差分线路的两个导体上。TVS(瞬态电压抑制器)二极管通常用于此类应用。它们具有非常快的响应时间,并在短时间内将电压限制在某个值。

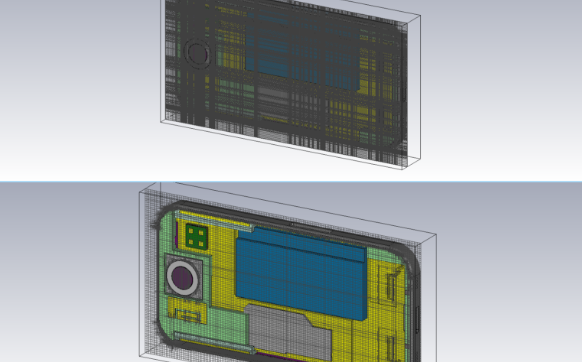

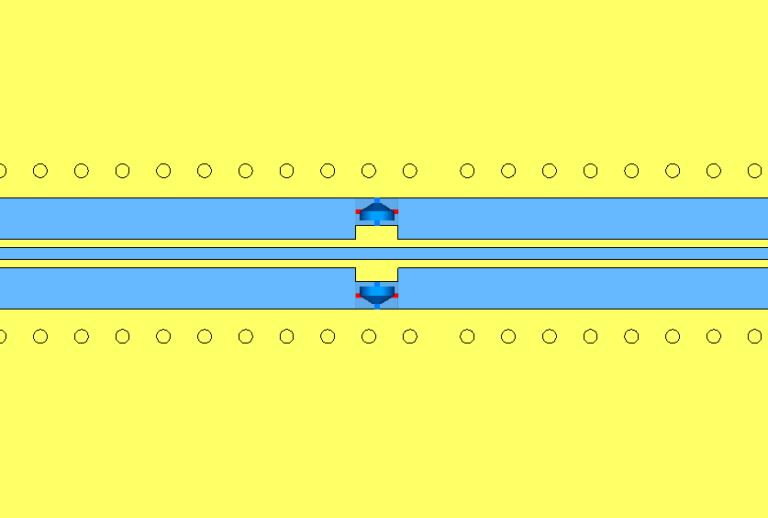

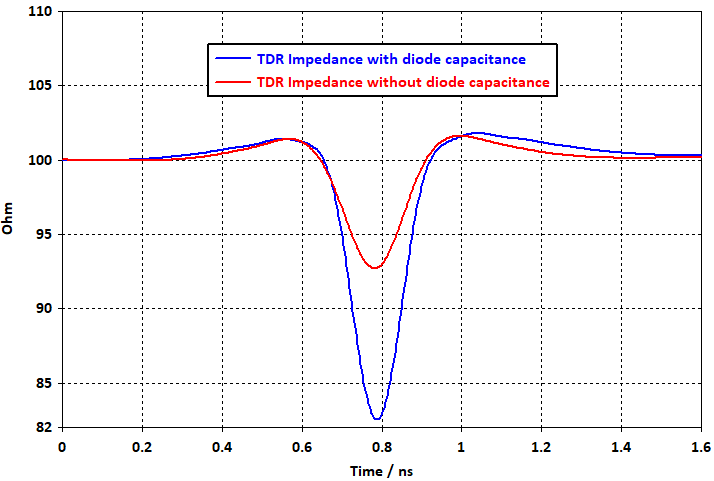

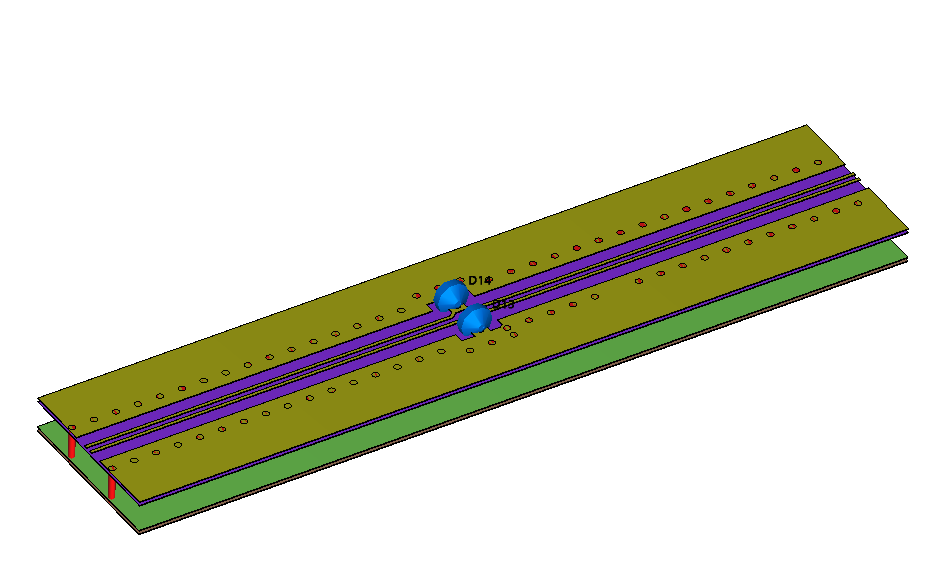

对于 6 Gbps 的高速数据速率,使用具有低寄生元件的小元件封装尺寸非常重要。对于分析的几何结构,我们使用了 Nexperia 的 ESD 保护二极管 PESD5V0C1BLS-Q [1]。该器件的最大二极管电容为 0.3 pF,封装尺寸为 1 mm x 0.6 mm x 0.47 mm。在仿真中,ESD 二极管使用“集总元件”定义。它们仅通过其寄生能力进行复制。“集总元件”是 CST 内部元件,可以表示 R、L、C 分量。图 2 显示了包括 ESD 二极管在内的差分线的仿真模型。

图 2.带 ESD 二极管的差分线仿真模型

在图 2 中,可以看出差分信号线上 ESD 元件的着陆焊盘比走线宽。显然,这个特定位置的横截面变化会导致线路阻抗变化。根据阻抗变化的大小,会对信号完整性产生影响。

布局前 TDR 仿真

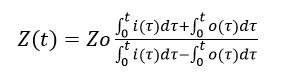

分析传输线上线路阻抗的一种众所周知的方法是时域反射法 (TDR)。它的工作原理类似于雷达原理,其中传输脉冲并在输入侧记录反射信号。通过评估反射信号,可以获得有关阻抗曲线的信息。CST STUDIO SUITE还可以使用时域或频域求解器执行 TDR 仿真。对于这个布局前的研究,我们使用了频域求解器。这是合理的,因为离散化的结构相对简单,而且与波长相比,它的尺寸很小。由于频域求解器仅提供 S 参数结果,因此我们通过对回波损耗 S 参数 S11 进行后处理来计算 TDR 结果。将高斯信号定义为输入信号后,可以根据回波损耗信息重建输出信号。我们通过应用公式 1 来计算 TDR。

仿真中定义的最大频率范围为 8.4 GHz,对应于 104 ps 的 10%-90% 上升时间。

图 3.高斯脉冲的时间积分

CST Studio Suite 可以使用基于模板的后处理 “TDR calculation from S-Parameter” 自动执行此计算,如图 4 所示。

图 4.基于 S 参数的 TDR 计算的模板后处理

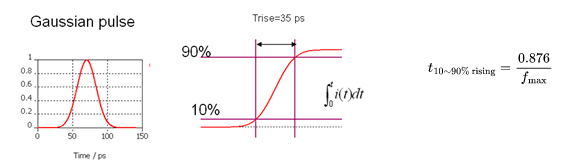

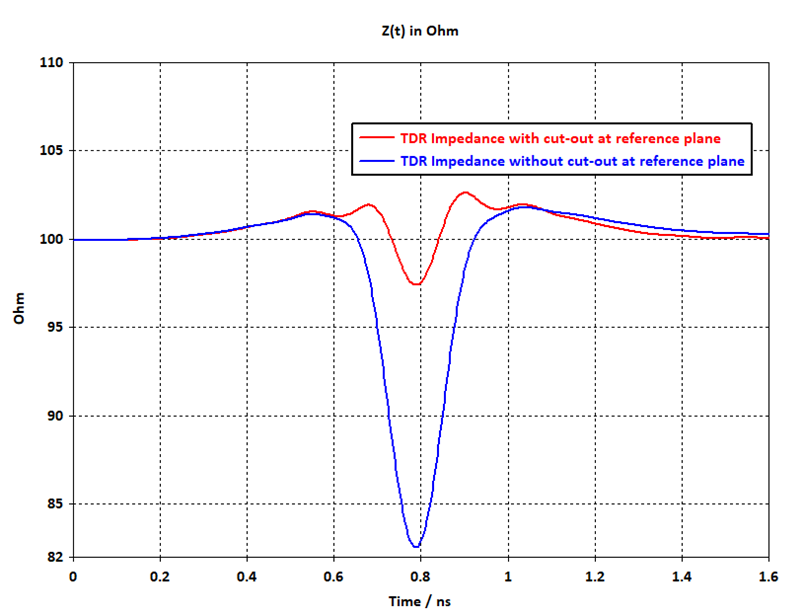

尽管二极管电容值相当小 (0.3 pF),但在执行 TDR 仿真时必须考虑它。它降低了标称线路阻抗 (100 Ω)。图 5 说明了 – 不考虑此电容的比较。

图 5.带二极管电容和不带二极管电容的 TDR 模拟

布局修改

在设计高速数据通道时,通常将允许的最大阻抗变化设置为 ± 10%。对于 100 Ω 的参考阻抗,我们可以从图 5 中看出,曲线下降到

83 Ω.这将不符合要求的下限 (90 Ω)。为了满足阻抗要求,必须围绕 ESD 二极管位置进行布局优化。

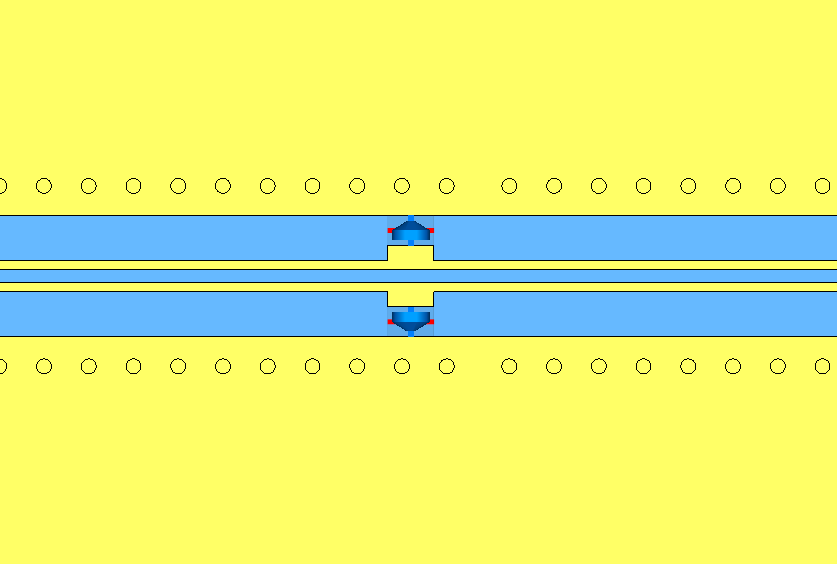

由于 ESD 二极管电容会降低该区域的线路阻抗,因此有必要通过减小传输线每米的电容来补偿这种影响。最有效的方法是切掉 ESD 二极管下方的参考平面。通过仿真可以找到凹陷地面区域的最佳大小。图 6 显示了经过多次仿真迭代后,针对特定层结构的修改后参考平面的优化配置。

图 6.带切口的参考平面(GND 通孔不可见)

相应的阻抗曲线改善如图 7 所示。

图 7.在参考平面上有开孔和无开孔的阻抗比较

请注意,接地层的开孔可能允许来自其他开关或干扰信号的串扰。因此,建议不要在此 cutout 下方布线任何敏感信号线。在 PCB 布局设计工具中,这可以通过创建限制/禁止区域来确保。

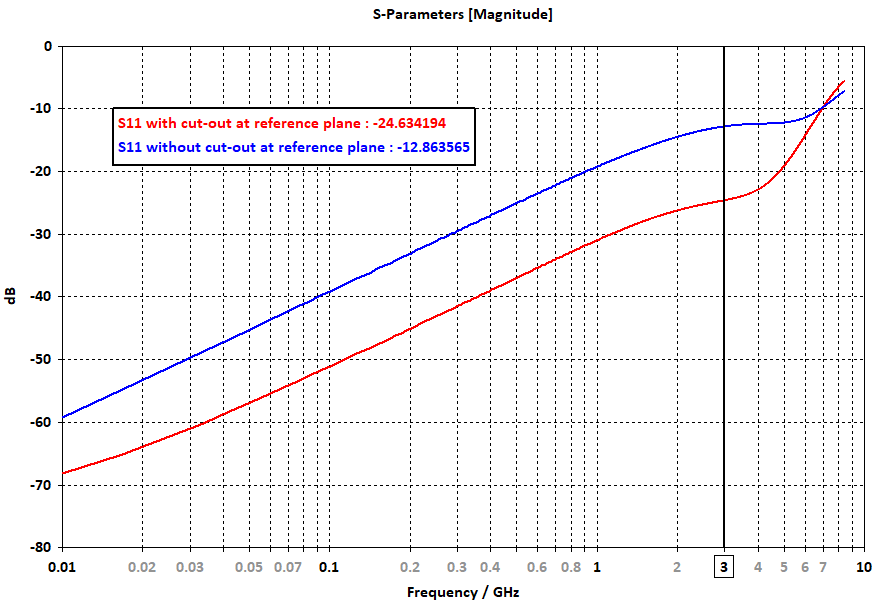

线路阻抗的改善也可以从回波损耗 S 参数 S11 中看出

(图 8)。可以观察到回波损耗改善了约 12 dB。这也意味着信号完整性的提高。

图 8.回波损耗 (S11) 在参考平面有切口和没有切口时的比较

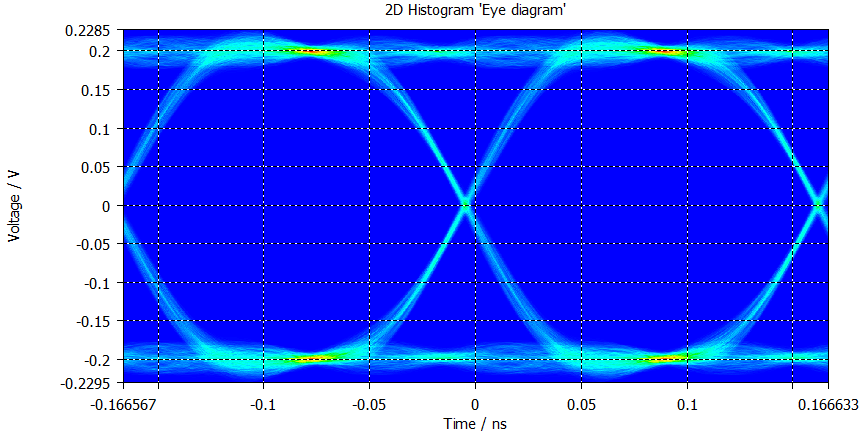

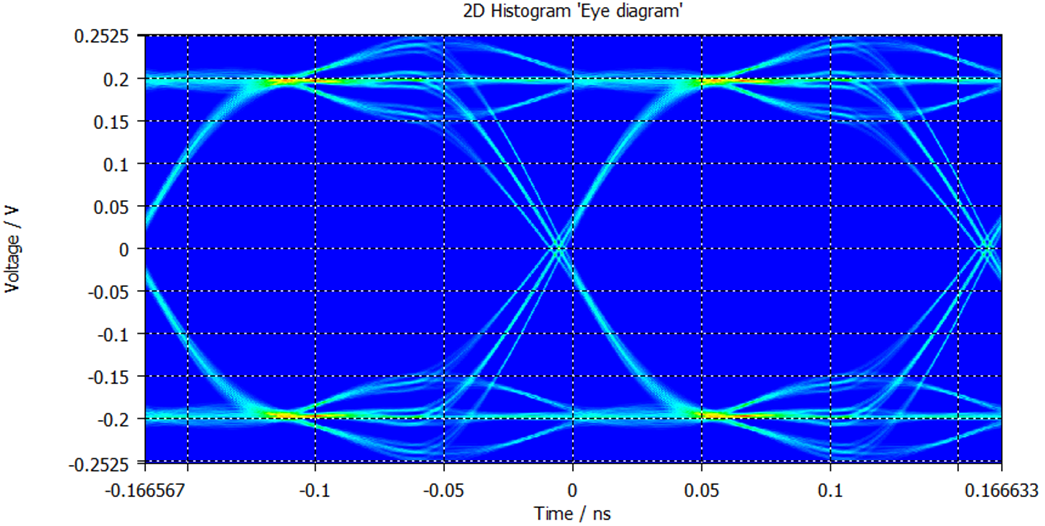

通过比较眼图结果,也可以证明凹陷参考平面的信号完整性行为更好。使用的数字伪随机位序列 (PRBS) 具有以下特性:

PRBS12

差分电压电平 ± 200 mV

上升和下降时间为 80 ps,周期长度对应于 3 GHz

图 9 和图 10 显示了两种布局的眼图。

图 9.带有参考平面切口的眼图。

图 10.没有参考平面切口的眼图。

测量比较

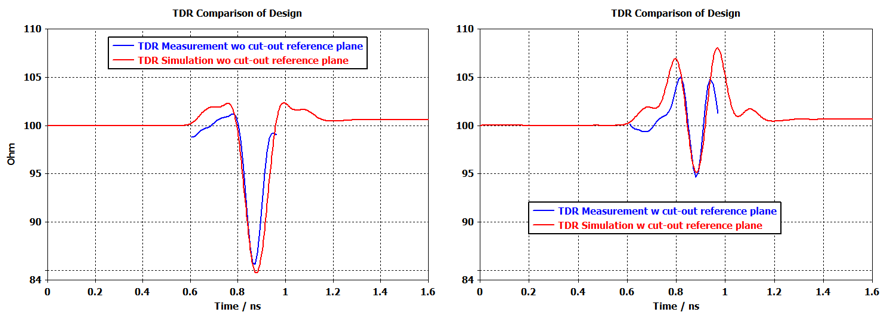

为了确认仿真结果,已经创建了一个具有优化参数(由 CST Studio Suite 仿真找到)的 PCB 布局。TDR 阻抗测量是使用 Sequid 的差分 TDR 测量系统进行的。在测量过程中,传输线通过 SMA 插座连接。对于仿真,无需考虑连接器,因为它们只会增加计算能力和时间,而不会影响 ESD 二极管周围的线路阻抗。差分线的末端可以保持开放状态。

用于测量的制造 PCB 原型是标准的 FR-4 板,具有 4 层,总厚度约为 1.6 mm。差分对尺寸与布局前研究中使用的尺寸略有不同,但参考平面切口尺寸保持不变。图 11 显示了 CST Studio Suite 用于测量比较的 PCB 布局原型的一部分。

图 11.CST MWS 内的 PCB 原型模型。

测量和仿真之间的线路阻抗结果比较如图 12 所示。与测量的良好一致性证实了使用 CST MWS 进行仿真。

图 12.测量和仿真之间的阻抗比较。

结论

为了传输高速数据信号,必须为整个高速数据通道实现平滑的线路阻抗曲线。信号完整性要求通常±参考阻抗的 10%。在这篇博客文章中,我们介绍了使用 CST Studio Suite 对这种传输线进行 3D 布局仿真和优化。我们展示了在布局前阶段使用这种仿真工具的好处,尤其是在开发时间方面。我们表明,在优化过程中尊重 ESD 二极管分量(电容信息)以获得更真实的结果非常重要。最后,仿真和测量之间的良好一致性证实了 CST Studio Suite 仿真结果的准确性。

引用

[1] https://www.nexperia.com/products/esd-protection-tvs-filtering-and-signal-conditioning/automotive-esd-protection-and-tvs/automotive-esd-protection/PESD5V0C1BLS-Q.html

获取正版软件免费试用资格,有任何疑问拨咨询热线:400-886-6353或 联系在线客服

未解决你的问题?请到「问答社区」反馈你遇到的问题,专业工程师为您解答!